基于TLC5510的數(shù)據(jù)采集系統(tǒng)設(shè)計

關(guān)鍵字:數(shù)據(jù)采集卡, 高速數(shù)據(jù)采集卡, 采集卡, 高速采集卡, USB數(shù)據(jù)采集卡, USB采集卡

1 TLC5510簡介

TLC5510是美國德州儀器(TI)公司的8位半閃速架構(gòu)A/D轉(zhuǎn)換器。采用CMOS工藝,大大減少比較器數(shù)。TLC5510最大可提供20 Ms/s的采樣率,可廣泛應(yīng)用于高速數(shù)據(jù)轉(zhuǎn)換、數(shù)字TV、醫(yī)學(xué)圖像、視頻會議以及QAM解調(diào)器等領(lǐng)域。TLC5510的工作電源為5 V,功耗為100 mW(典型值)。內(nèi)置采樣保持電路,可簡化外圍電路設(shè)計。TLC5510具有高阻抗并行接口和內(nèi)部基準(zhǔn)電阻,模擬輸入范圍為0.6 V~2.6 V。

1.1 引腳功能描述

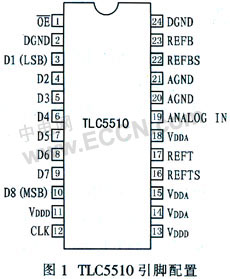

TLC5510采用24引腳的貼片封裝,其引腳配置如圖1所示,各引腳功能描述如下:

AGND:模擬信號地;

ANGLOG IN:模擬信號輸入端;

CLK:時鐘輸入端;

DGND:數(shù)字信號地;

D1~D8:數(shù)據(jù)輸出端。D1為數(shù)據(jù)低位,D8為數(shù)據(jù)高位;

OE:輸出使能端。OE為低電平時數(shù)據(jù)端有效,否則數(shù)據(jù)端為高阻態(tài);

VDDA:模擬電路工作電壓;

VDDD:數(shù)字電路工作電壓;

REFTS:內(nèi)部參考電壓。當(dāng)內(nèi)部分壓器輸出額定2 V基準(zhǔn)電壓時,該端短路至REFT;

REFT:參考電壓(T代表Top為2.6 V);

REFB:參考電壓(B代表Bottom為0.6 V);

REFBS:參考電壓。當(dāng)內(nèi)部分壓器產(chǎn)生2 V的額定基準(zhǔn)電壓時,該端短路至REFB。

1.2 典型應(yīng)用電路

TLC5510的基準(zhǔn)電源有多種接法,根據(jù)不同場合選擇適當(dāng)基準(zhǔn)電源,利用內(nèi)部基準(zhǔn)源,TLC5510典型應(yīng)用電路如圖2所示。由于其測量范圍為0.6 V~2.6 V(即:TLC5510在轉(zhuǎn)換時模擬輸入0.6 V時對應(yīng)數(shù)字輸出00 000 000,2.6 V對應(yīng)的數(shù)字輸出11111 111),因此輸入信號在進(jìn)入TLC5510之前要塒其處理,要使該輸入信號處于量程內(nèi),應(yīng)加入一個1.6 V的直流分量。

2 基于TLC5510的數(shù)據(jù)采集設(shè)計

2.1 兩級采樣

TLC5510雖采樣率高,但受干擾嚴(yán)重。基于上述特點,將TLC5510運用于寬頻數(shù)字示波器的數(shù)據(jù)采集。為了提高抗干擾能力,專門設(shè)計一個有源晶振模塊為TLC5510提供采樣時鐘,但導(dǎo)致采樣率不可調(diào)。為了解決這個問題,采用兩級采樣。第一級采樣為控制A/D轉(zhuǎn)換器對外圍的電信號高速采樣,并將其采樣保存到FPGA內(nèi)部寄存器,該級采樣率恒定不變,并由硬件設(shè)計實現(xiàn);第二級采樣為軟件采樣,即由FPGA采樣控制模塊從寄存器中提取第一級采集結(jié)果,該級采樣率是可調(diào)的。

2.2 等效采樣

根據(jù)奈奎斯特定律,采樣頻率高于信號頻率的兩倍就可恢復(fù)原波形。當(dāng)采樣頻率等于或小于信號頻率可采用等效采樣,在不同周期獲取不同相位的幅值,根據(jù)相位將幅值連續(xù)排列即可復(fù)原波形。

采用內(nèi)觸發(fā)采樣,即巾被測信號的某相位點位為觸發(fā),然后存儲。其實現(xiàn)過程:每一個完整的采樣需采集256個點,每一個采樣點都是由相同電平觸發(fā),觸發(fā)后啟動FPGA內(nèi)部的計數(shù)器,對高頻脈沖記數(shù),脈沖數(shù)不同,代表相位也不相同。經(jīng)過256個周期,就可采集256個不同的相位點。

3 基于FPGA的等效采樣

3.1 實現(xiàn)方案

該系統(tǒng)沒計采用延遲法來實現(xiàn)等效采樣。如圖3所示,設(shè)輸入信號f(t)的周期為T(頻率為f),若將f(t)的一個周期T以△t等分,在時間t1進(jìn)行第一次取樣,為了采集到下一個相位點,在時間t2進(jìn)行第二次采樣,tl~t2可相隔多個信號周期。假設(shè)m個,則相鄰兩個采樣脈沖的時間間隔為(mT+△t)。如此類推,以下3個采樣點則分別在t3,t4,t5時刻采樣。在每個觸發(fā)位置延時N△t(N=0,1,2,3…)后存儲采樣,即可合成一個完整波形。這種方法控制方便,通過FPGA完成整個觸發(fā)、延時、采樣和存儲功能,但對觸發(fā)電路和延時電路要求很高。

3.2 硬件電路設(shè)計

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750