一種新型高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

關(guān)鍵字:采集卡價(jià)格, USB數(shù)據(jù)采集卡價(jià)格, USB采集卡價(jià)格, USB高速數(shù)據(jù)采集卡價(jià)格

摘要: 介紹了一種基于USB2.0接口的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)。該采集系統(tǒng)能夠?qū)?A class=contentlabel >雷達(dá)接收機(jī)送來(lái)的信號(hào)進(jìn)行高速的采集,然后通過(guò)USB接口,將采集到的數(shù)據(jù)送到計(jì)算機(jī),經(jīng)由上層軟件對(duì)數(shù)據(jù)進(jìn)行處理分析。

關(guān)鍵詞: USB2.0;FPGA;高速數(shù)據(jù)采集;雷達(dá)接收機(jī)

引言

在雷達(dá)接收機(jī)的測(cè)試和維護(hù)中,經(jīng)常需要對(duì)數(shù)據(jù)進(jìn)行采集,然后將采集到的數(shù)據(jù)送入計(jì)算機(jī)進(jìn)行分析處理。鑒于對(duì)數(shù)據(jù)實(shí)時(shí)采集的需求,對(duì)采集系統(tǒng)提出三方面的要求:第一,接口簡(jiǎn)單靈活且有較高的數(shù)據(jù)傳輸率;第二,采集的數(shù)據(jù)能夠快速處理并能方便提取原始數(shù)據(jù);第三,數(shù)據(jù)采集裝置具備多路數(shù)據(jù)采集能力。對(duì)于一些特殊應(yīng)用,甚至需要整個(gè)數(shù)據(jù)采集系統(tǒng)能夠方便攜帶。

傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大多通過(guò)PCI總線完成數(shù)據(jù)的傳輸,但PCI總線存在嚴(yán)重缺陷:受限于計(jì)算機(jī)插槽數(shù)量和中斷資源;不便于連接與安裝;易受機(jī)箱內(nèi)電磁環(huán)境的影響。這些問(wèn)題遏制了基于PCI總線的數(shù)據(jù)采集系統(tǒng)的進(jìn)一步開(kāi)發(fā)和應(yīng)用。因此,需要一種更為簡(jiǎn)便通用的方式來(lái)完成采集系統(tǒng)和計(jì)算機(jī)的數(shù)據(jù)的交互。

考慮到現(xiàn)代計(jì)算機(jī)上大都配備了USB接口,且USB支持即插即用,安裝方便,易于擴(kuò)展,USB2.0能夠達(dá)到480Mb/s的理論傳輸速度,非常適合在高速數(shù)據(jù)采集系統(tǒng)中應(yīng)用。因此,通過(guò)USB接口來(lái)完成數(shù)據(jù)傳輸是一個(gè)很好的替代方案。出于上述考慮,筆者設(shè)計(jì)了一個(gè)基于USB2.0接口的高速數(shù)據(jù)采集系統(tǒng),通過(guò)實(shí)際測(cè)試,該系統(tǒng)可以很好的完成數(shù)據(jù)采集的功能。

數(shù)據(jù)采集系統(tǒng)電路設(shè)計(jì)

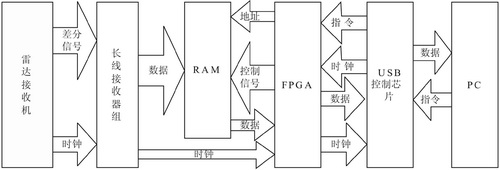

高速數(shù)據(jù)采集系統(tǒng)框圖如圖1所示。系統(tǒng)整體的設(shè)計(jì)思路如下:計(jì)算機(jī)將采集指令(包括數(shù)據(jù)格式,數(shù)據(jù)長(zhǎng)度,FPGA控制指令等)送給USB控制芯片,USB控制芯片通過(guò)固件程序?qū)χ噶钸M(jìn)行簡(jiǎn)單的格式判定,然后將判定后正確的指令送給FPGA,FPGA對(duì)指令進(jìn)行譯碼,獲得需要采集的數(shù)據(jù)的長(zhǎng)度,以及采集的地址和控制信號(hào),控制RAM來(lái)完成數(shù)據(jù)的采集存儲(chǔ)。雷達(dá)接收機(jī)送過(guò)來(lái)的數(shù)據(jù)和時(shí)鐘信號(hào)經(jīng)過(guò)長(zhǎng)線接收器組以后,由差分信號(hào)變?yōu)槠胀ǖ臄?shù)字信號(hào),時(shí)鐘信號(hào)送入FPGA,經(jīng)過(guò)處理后,用來(lái)控制數(shù)據(jù)的采集時(shí)刻,數(shù)據(jù)先存入RAM,待完成所需數(shù)目的采集以后,再通過(guò)USB控制芯片送給計(jì)算機(jī),完成數(shù)據(jù)的后期處理和顯示。

圖1 高速數(shù)據(jù)采集系統(tǒng)框圖

圖2為FPGA與USB控制芯片的連接圖,電路中FPGA選用EP1C3T144C8,USB控制芯片選用Cypress 公司的CY7C68013。USB_Ready 為USB芯片狀態(tài)標(biāo)志,低電平有效;FPGA_Ready為FPGA芯片狀態(tài)標(biāo)志,低電平有效;USB_Clk為USB向FPGA傳送指令的指令時(shí)鐘,USB_Data 為USB傳送給FPGA的控制指令;FD[15:0]為USB 與FPGA交互的數(shù)據(jù)。

圖2 FPGA與USB控制芯片的電路連接圖

FPGA與USB芯片之間的通信流程如下:

1、FPGA發(fā)送FPGA_Ready信號(hào)給USB控制芯片,表示FPGA

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號(hào):sun62169728

地址:北京市西城阜外百萬(wàn)莊扣鐘北里7號(hào)公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號(hào)-1 公備110108007750