使用邏輯分析儀時(shí)需要的注意事項(xiàng)

邏輯分析儀提供商已經(jīng)能讓這些設(shè)備的速度和功能與工業(yè)需求同步,但在很多情況下,從邏輯分析儀到目標(biāo)系統(tǒng)的物理連接(如探頭)可能成為性能瓶頸。

若邏輯分析儀所收到的信號被衰減,那么邏輯分析儀強(qiáng)大的觸發(fā)和分析工具也變得沒有任何意義。本文討論的問題也是工程師成功連接邏輯分析儀探頭所必須了解的基本問題。

幾十年來,工程師一直依賴邏輯分析儀,把它們作為主要的系統(tǒng)驗(yàn)證工具。隨著科學(xué)技術(shù)的發(fā)展,工程師所設(shè)計(jì)的數(shù)字系統(tǒng)的運(yùn)行速度不斷加快、指令更加復(fù)雜,從而也要求更為復(fù)雜的分析工具。

探頭的外形因子

在使用邏輯分析儀時(shí),設(shè)計(jì)工程師應(yīng)首先考慮到探頭的外形因子的類型。探頭的連接可分為兩類:一類是“已設(shè)計(jì)好(designed-in)”的連接,另一類是“事后設(shè)計(jì)的(after-the-fact)”的連接。

designed-in型邏輯分析儀探頭的測試點(diǎn)已被集成到最初設(shè)計(jì)中,基于連接器的探頭或無連接器探頭就是采用這種方式。在這種情況下,設(shè)計(jì)工程師在PCB上設(shè)計(jì)合適的焊盤,并將待信號連到這些焊盤上,這樣邏輯分析儀探頭就與待測點(diǎn)有較好互連。

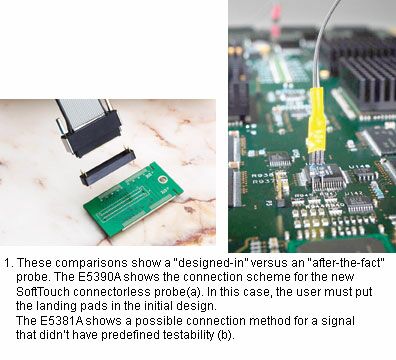

在基于連接器的探頭中包含了相互契入的連接器,而無連接器探頭則具有連接PCB上焊盤的壓縮互連(compression interconnect)(圖1a)。

|

after-the-fact型探頭應(yīng)用于可測試性能沒有集成到設(shè)計(jì)中的系統(tǒng),該系統(tǒng)通過一個(gè)包括一系列連接組件(焊接頭、接線夾等)的單個(gè)探頭尖(probe tip)來與待測系統(tǒng)連接。最常見的after-the-fact探頭一般利用如圖1b所示的“flying-lead(飛線)”探頭。

探頭的電氣負(fù)載

任何探頭的目標(biāo)都是給僅給系統(tǒng)帶來最小的電氣負(fù)載。如果探頭對系統(tǒng)性能帶來太多影響,探頭就無法幫助設(shè)計(jì)工程師驗(yàn)證系統(tǒng),因?yàn)橄到y(tǒng)故展可能完全是由于探頭而引起的。

負(fù)載具有產(chǎn)生兩個(gè)主要影響:首先,它降低目標(biāo)PCB上的信號質(zhì)量,導(dǎo)致系統(tǒng)發(fā)生失效。其次,它會降低進(jìn)入邏輯分析儀中被測波形的信號質(zhì)量──這會在評估時(shí)產(chǎn)生消極錯(cuò)誤。為了避免這些問題,設(shè)計(jì)工程師必須了解探頭的結(jié)構(gòu)。

探頭的阻抗通常很高。探頭針(probe tip)電路由一個(gè)20kΩ的電阻構(gòu)成。低頻下,探頭阻抗等于該電阻的阻值。隨著頻率的提高,探頭內(nèi)的寄生電容開始降低其阻抗。阻抗根據(jù)標(biāo)準(zhǔn)RC響應(yīng)而變化,這也是目標(biāo)系統(tǒng)所關(guān)注的,因?yàn)楫?dāng)探頭阻抗接近系統(tǒng)阻抗時(shí),由探頭形成的分壓器的作用就不能被忽視了。低阻抗將吸收大部分信號并導(dǎo)致系統(tǒng)發(fā)生故障。

探頭的電容大小主要由互相連接的結(jié)構(gòu)決定。例如,若目標(biāo)信號和探頭頭的電阻之間有一個(gè)非常大的連接器,則這個(gè)連接器會給探頭負(fù)載增加一個(gè)大容量的電容。相反,采用小連接器則將減小探頭電容。

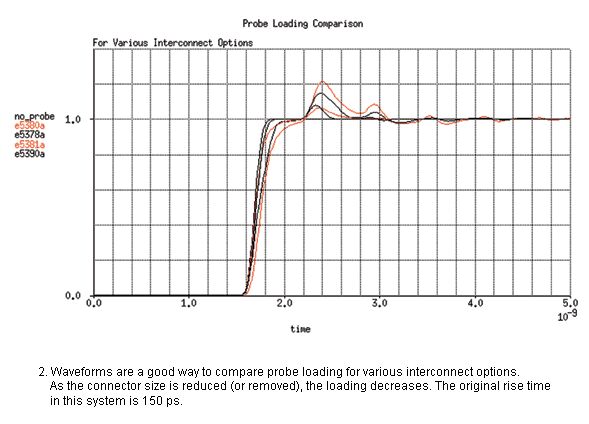

針對更輕電氣負(fù)載應(yīng)用的最新探頭是“無連接器”探頭。在無連接器探頭中,測試焊盤被置于目標(biāo)系統(tǒng)上。邏輯分析器探頭具有連接目標(biāo)系統(tǒng)的壓縮互連特性。通過從電氣通道中去除物理連接器,其通道上的電容非常低(見表)。圖2顯示了多種探頭外形因子的等效集總電容,以及這些探頭對上升時(shí)間為150ps的系統(tǒng)的影響。

|

探頭上的信號質(zhì)量

正如前面提到的,探頭尖上的信號質(zhì)量非常重要,因?yàn)樗赡軐?dǎo)致邏輯分析儀出現(xiàn)錯(cuò)誤結(jié)果。這也是讓驗(yàn)證團(tuán)隊(duì)屢屢碰壁的一個(gè)原因,因?yàn)樗麄儼l(fā)現(xiàn)他們花了很多時(shí)間去調(diào)試的問題事實(shí)上不存在。為避免出現(xiàn)這種情況,必須考慮到探頭尖上的信號質(zhì)量。

除了減少探頭的容性負(fù)載外,另外一個(gè)重要因素就是探頭的位置。在對有多種終端匹配的電路進(jìn)行探測時(shí),這一點(diǎn)顯得更為重要。對于某些終端匹配,接收器所觀察到的信號質(zhì)量已足夠好,但該走線上其它任何點(diǎn)上的信號就可能差到不可接受了。

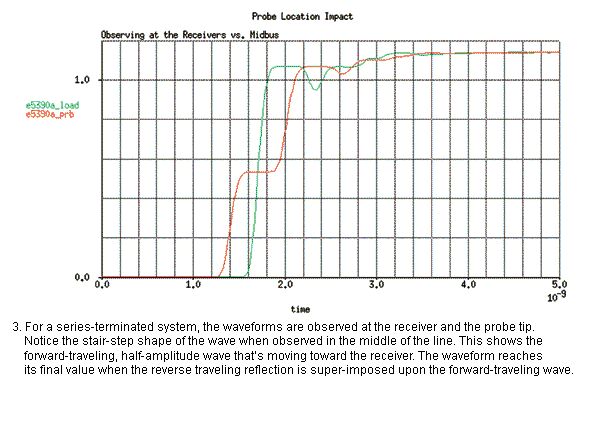

為解釋這一點(diǎn),我們假定有一個(gè)帶串聯(lián)終端匹配的傳輸線。串聯(lián)終端匹配的原理是感應(yīng)波形在一瞬間在終端電阻和傳輸線特征阻抗之間進(jìn)行分配。幅值為一半的波形沿線傳輸?shù)浇邮掌鳌.?dāng)它到達(dá)接收器時(shí),它已經(jīng)過100%的正反射,使該信號幅值增加1倍,這樣就回復(fù)到原波形的幅值。反射波以相反的方向傳輸,直到它被源端的終端電阻吸收,結(jié)束瞬時(shí)響應(yīng)。

盡管這樣的終端匹配使接收器上的波形非常好,但波形在走線上的每一點(diǎn)都呈階梯形。階梯波形并不適于邏輯分析儀,因?yàn)樵诖似陂g,該波形的幅值只有一半。邏輯分析儀不能分辨出它是邏輯“1”還是邏輯“0”。圖3顯示了這種情況下的波形。請注意,接收器端的這種波形有較高的信號質(zhì)量,而探頭尖上被測到的波形質(zhì)量則很是不可接受的。隨著信號速度上升,探頭尖上的信號質(zhì)量對成功測量越來越重要。

| ||||||||

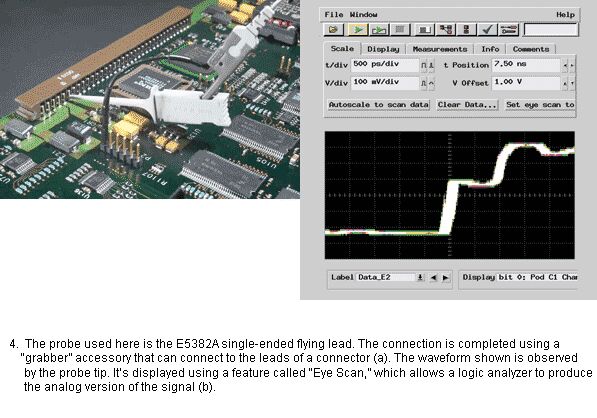

| 接地考慮 沒有良好接地是設(shè)計(jì)工程師進(jìn)行邏輯分析時(shí)另一個(gè)容易出問題的地方。探頭的地信號為被觀察的信號提供一個(gè)參考。 因?yàn)殡娏饕鲃?dòng),信號有變化,所以電氣信號必須有一個(gè)回流電流路徑。回流路徑常被認(rèn)為是阻值為0的理想導(dǎo)體。 當(dāng)其阻值不為0時(shí),在回流路徑的阻抗上將產(chǎn)生電壓降,從而降低邏輯分析儀測量到的信號幅值。 接地的目的是提供一個(gè)具有最小阻抗的回流路徑(或接地連接),從而讓邏輯分析儀觀察到原始的信號幅度。 一個(gè)常見的接地問題是地線太長。長地線上的串聯(lián)電阻會產(chǎn)生壓降。為避免這個(gè)問題,地線不能比信號線長太多,以便匹配信號和地之間的寄生電阻。 另一個(gè)常見的問題是接地回路的自感。當(dāng)回路由地線和信號線組成時(shí),在接地路徑中會形成一個(gè)與回路面積成比例的自感。由于電感具有與頻率相關(guān)的阻抗,它將降低系統(tǒng)的帶寬。在高頻情況下,這個(gè)字感將阻止電荷流過地線,從而減小帶寬。 為緩解這類問題,設(shè)計(jì)工程師應(yīng)盡量使接地回路盡可能小。當(dāng)使用基于連接器或無連接器的探頭時(shí),接地回路已預(yù)先確定。然而,若使用飛線探頭,通常使用電線來連接探頭和系統(tǒng),因而形成大的接地回路。 為避免這種回路,將地線和信號線絞合在一起形成一個(gè)對絞線。大多數(shù)飛線探頭現(xiàn)在都有連接附件,已解決這個(gè)問題。 當(dāng)探測時(shí)沒有采用足夠的接地時(shí)就會發(fā)生另一種情況。在一些探測配置中(如飛線探頭),地線數(shù)目由使用者決定。為理解這個(gè)問題,假定一個(gè)飛線設(shè)定16個(gè)信號線僅用一根地線連接。 此時(shí),所有16根信號線的回流電流必須通過單個(gè)地線連接。當(dāng)1個(gè)或2個(gè)信號回路通過地線時(shí),地線的自感應(yīng)足夠低,其上的壓降不會變大。但若是16根信號線,則回流電流就很大了,此時(shí)所產(chǎn)生的地線壓降不能忽略。 要解決這一問題就要求增加地線的數(shù)量,理想的情況是一根信號線對應(yīng)一根地線。地線的數(shù)量也與頻率成比例,但是建議不要用一根地線對應(yīng)兩根以上的信號線。 若操作者在使用邏輯分析儀時(shí)不能獲得準(zhǔn)確的數(shù)據(jù),首先要考慮的就是檢查地線。 如今有多種探頭可供選擇,有時(shí)很難決定采用哪種連接機(jī)制以確保探測成功。在某些情況下,甚至要知道哪些解決方案可用也很困難。下面將討論當(dāng)設(shè)計(jì)工程師采用錯(cuò)誤的探測解決方案時(shí)常犯的錯(cuò)誤。 選擇錯(cuò)誤的探測點(diǎn) 考慮前面提到的串聯(lián)終端配置系統(tǒng),該系統(tǒng)由背板上的驅(qū)動(dòng)IC和采用BGA封裝的接收器實(shí)現(xiàn)。使用者根據(jù)使用的方便,在引腳的背板連接器上對系統(tǒng)進(jìn)行探測。但是,正如前面已經(jīng)討論的那樣,在驅(qū)動(dòng)器上探測串聯(lián)終端配置系統(tǒng)將在邏輯分析儀的探頭尖產(chǎn)生一個(gè)階梯波形。圖4a顯示了探測連接方式,圖4b則是通過探頭檢測到的最終波形。

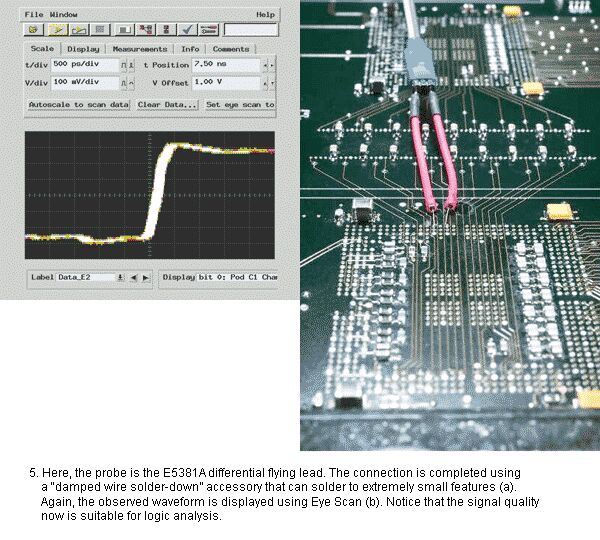

毫無疑問這樣的波形是不可接受的。解決的辦法是直接在接收器上進(jìn)行探測。BGA封裝最近的物理探測點(diǎn)可能是PCB底面的引線過孔焊盤。圖5a展示了一種新的連接方案,它直接用焊料將飛線連接到BGA的引線過孔焊盤。圖5b是測試到的信號波形。

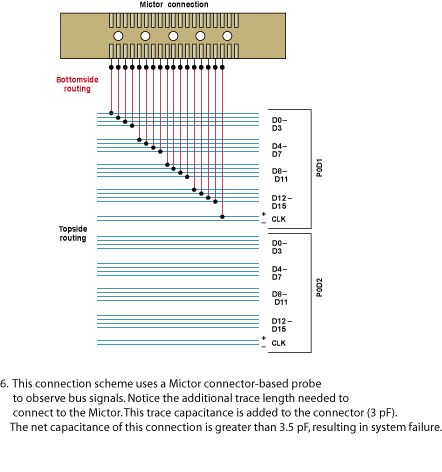

使用錯(cuò)誤的連接方法 假設(shè)用邏輯分析儀觀察一個(gè)系統(tǒng)的PCB上兩個(gè)器件之間的信號。該信號走線布在PCB表層,若負(fù)載超過3.5pF,則會導(dǎo)致系統(tǒng)失效。設(shè)計(jì)工程師利用基于Mictor連接器的探頭E5380A來觀察信號。 由于連接器的管腳分布和結(jié)構(gòu),信號不能用過它直接連接。這迫使設(shè)計(jì)工程師將連接器放在走線層,并對每個(gè)信號增加過孔。于是,對連接器的走線連接利用另外一層PCB層完成,其走線方向與原始信號的走線垂直。圖6顯示了該連接器的布線圖。

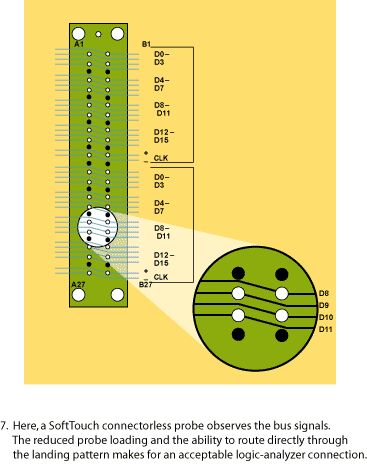

現(xiàn)在考慮一個(gè)替代方案,即采用E5390A軟接觸無連接器探頭。此時(shí)可將信號連接到探測點(diǎn)的測試焊盤(見圖7),這意味著不會給系統(tǒng)增加額外的走線電容。該探頭的網(wǎng)絡(luò)電容為0.7 pF,通過采用這種連接,可在不導(dǎo)致系統(tǒng)失效的情況下進(jìn)行邏輯分析。

作者:Brock J. LaMeres,Kenneth Johnson,安捷倫科技公司 |

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750