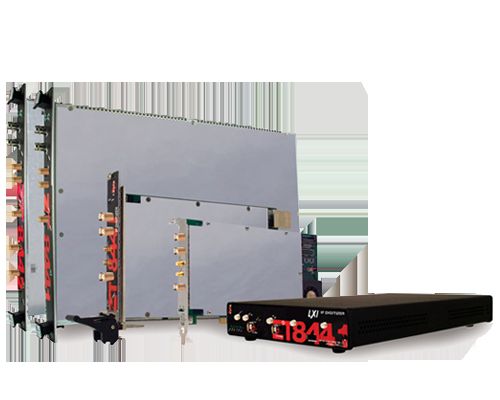

射頻和無線通訊測試設備

射頻和無線通訊測試設備

射頻測試系列:

|

型號

|

頻率范圍

|

瞬時帶寬

|

實時信號處理

|

采樣速率

|

ADC

|

動態(tài)范圍

|

輸入

|

內(nèi)存

|

信號范圍

|

|

DC to 1GHz

|

100 Hz to 160 MHz

|

FPGA-based digital down conversion (DDC) with fractional resampling

|

100 S/s to 400 MS/s

|

Dual 400 MS/s 16 bit

|

>80 dBc

|

RF or Dual I/Q

|

512 MB (up to 128 MiSamples of complex I/Q data pairs)

|

+10 dBm max

|

|

|

型號

|

頻率范圍

|

瞬時帶寬

|

實時信號處理

|

采樣速率

|

ADC

|

動態(tài)范圍

|

輸入

|

內(nèi)存

|

信號范圍

|

|

DC to 300MHz

|

100 Hz to 160 MHz

|

FPGA-based digital down conversion (DDC) with fractional resampling

|

100 S/s to 400 MS/s

|

Dual 400 MS/s 14-bit

|

>80 dBc

|

2 or 4 Differential

|

512 MiB

|

+ 10 dBm, 0 dBm, -10 dBm, -20 dBm

|

|

|

型號

|

頻率范圍

|

頻率分辨率

|

交換速度

|

不同的 I/Q輸入

|

瞬時帶寬

|

在100 kHz 偏移下相位噪聲

|

動態(tài)范圍

|

RF 電平范圍

|

|

|

DC to 6 GHz

|

1 Hz

|

<1 ms

|

+10 dBm to -20 dBm

|

160 Mhz

|

< -125 dBc/Hz @ 1 GHz

|

>80 dBc

|

+20dBm to -120dBm

|

|

北京迪陽世紀科技有限責任公司 版權所有 ? 2008 - 2018 著作權聲明

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750

售價:¥0

售價:¥0